**BPCRT2-1**

# **BIT-MAP GRAPHIC DISPLAY CONTROLLER**

### GENERAL DESCRIPTION

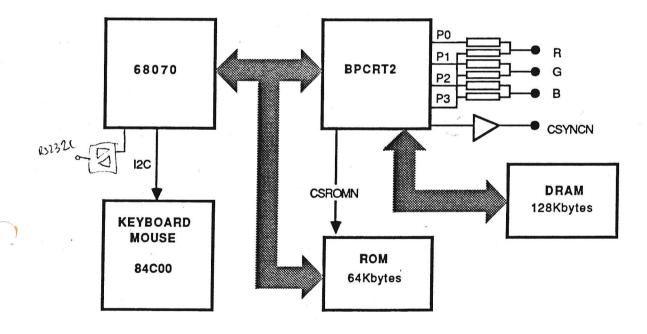

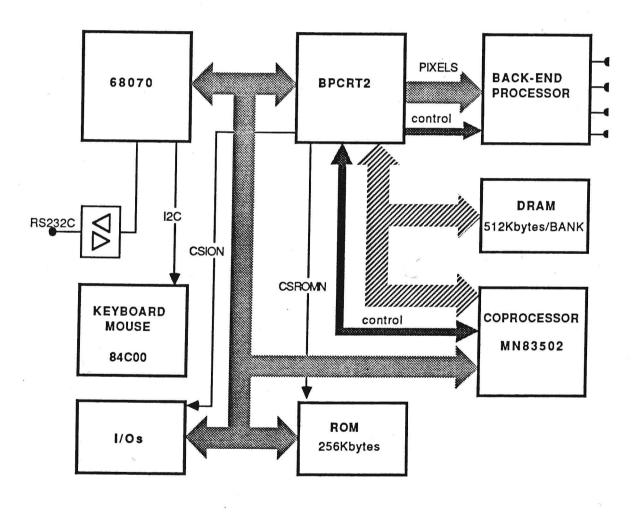

The BPCRT2 is a CMOS Color Display controller intended for cost effective bit-map oriented applications. Display resolution and number of bits per pixel are software programmable.

The device can drive directly up to 2 Megabytes of memory and provides the necessary refresh for the DRAM devices. In order to minimize the number of integrated circuits necessary in a minimal application, several system control functions are also integrated. Used with the 68070 in a minimal configuration, it controls the access to the System/Video DRAM, to the System ROM and to the I/O devices.

A high speed pixel manipulation circuit can accelerate the image manipulation compared to performing this by the central processor alone. An interface for a graphic co-processor is implemented to allow very high speed manipulation of the video memory contents.

### **FEATURES**

- Full Bit-Map organisation

- Capability to display Run-Length coded files

- Direct interface for 68000 compatible CPUs

- Up to 768 x 560 screen resolution

- 4 or 8 bits per picture element

- Mosaic effect

- Shift register for up to 15 MHz pixel rate

- On-chip oscillator

- Synchro generator for 50 and 60 Hz scan

- Double frequency scan

- Synchronisation with external video

- 1.5 Megabyte DRAM direct drive

- 0.5 Megabyte ROM control

- Reset sequencer, Watch-Dog timer

- Fast 16-bit pixel test-and-modify logic (pixblt)

- CMOS technology

- Surface Mounting Device package

### **APPLICATIONS**

- Home Computer

- Personal Computers

- Home entertainment

- Intelligent color terminals

- Graphics/text I/O systems

### PACKAGE

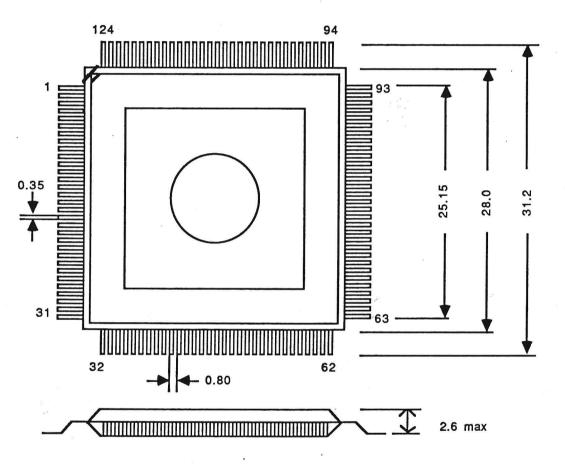

- 124-pin QUAD FLAT PACK plastic

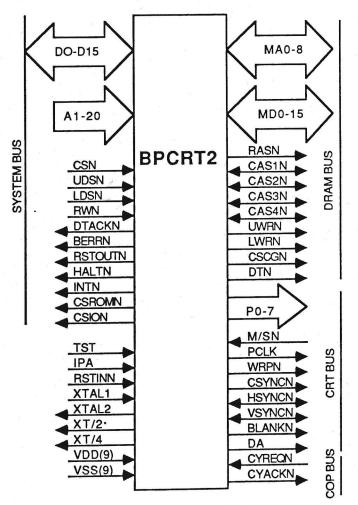

FIGURE 1: : LOGICAL PIN DESCRIPTION

PHILIPS

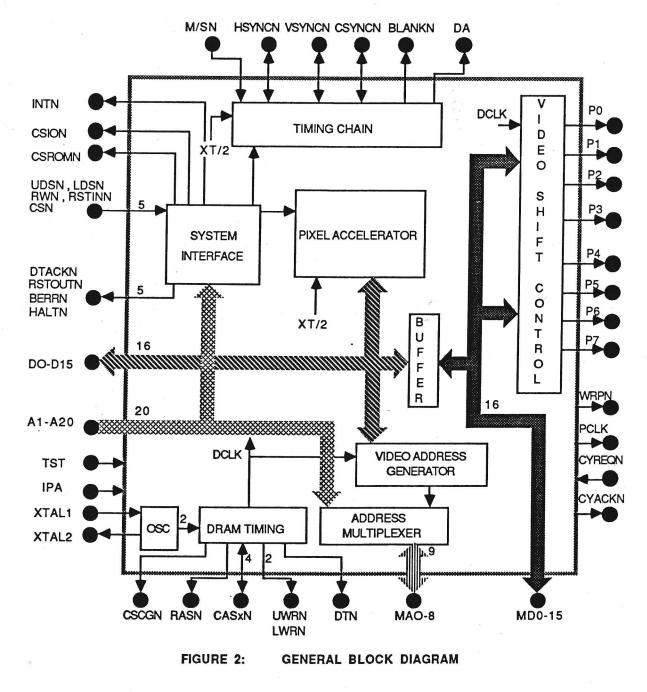

### **BLOCK DIAGRAM**

The following diagram describes the general organisation of the device.

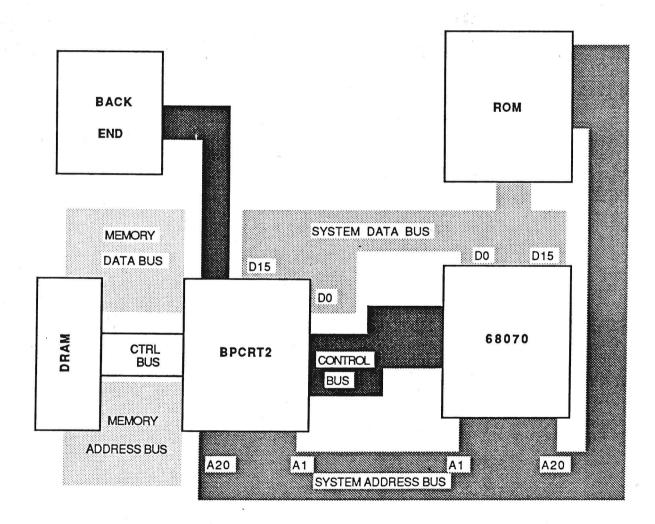

The connection to the system bus is made via 16 bidirectional Data lines, 20 Address lines and CONTROL lines. The connection to the Dynamic RAMs is made via 8 or 9 ADDRESS lines (MA bus), 16 Bidirectional DATA lines (MD bus) and control signals.

The video output is made of 8 Video DATA lines and 2 control lines.

The pixel accelerator is accessable both from the system bus, eg. using the CPU, and from the memory bus, eg. using the coprocessor interface.

PHILIPS

NOVEMBER

Electronic components

TARGET SPECIFICATION

X pulling RSTOUT, MALT, REPRESENT

Page n° 3

# BPCRT2-1

### **PIN ASSIGNEMENT**

| Name      | , I/O            | pin nun                       | nber Description                                                                                                                                                                                       |

|-----------|------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM BU | JS               |                               |                                                                                                                                                                                                        |

| A1-A20    | I                | 34-33<br>30-18<br>16<br>14-11 | System ADDRESS lines. Provides the system address for access from the system bus. Must be stable when UDS or/and LDS go Low.                                                                           |

| D0-D15    | 1/0              | 42-45<br>47<br>49-51<br>64-71 | Bidirectional three-state DATA bus. Used to transfer DATA between system bus<br>and BPCRT2. Must be stable when UDSN or LDSN are asserted during write<br>access. Driven by BPCRT2 during Read cycles. |

| UDSN      | ĵ <b>i</b>       | 41                            | Upper Data Stobe. Active low. When asserted, UDSN indicates that data is being addressed on D0 to D7.                                                                                                  |

| LDSN      | , I <sup>°</sup> | 40                            | Lower Data Stobe. Active low. When asserted, LDSN indicates that data is being addressed on D8 to D15.                                                                                                 |

| R/WN      | I                | 39                            | Read/Write. This input indicates the direction of tranfer on the system bus. When low, indicates Data is to be written into BPCRT2 controlled resources.                                               |

| CSN       | I                | 52                            | Chip Select. Active Low. Validates address decode for system access, must be low to access BPCRT2 controlled resources.                                                                                |

| DTACKN    | 0                | 38                            | DATA Transfer Acknowledge signal. Active Low, open drain. Asserted by BPCRT2 when the system bus cycle can be continued.                                                                               |

| RSTOUTN   | 0                | 35                            | RESET Output. Active Low, open drain. Asserted by the BPCRT2 Reset Sequencer during the reset procedure.                                                                                               |

| HALTN     | Ο                | 36                            | HALT line Output.Active Low, open drain. Asserted by the BPCRT2 Reset Sequencer during the reset procedure.                                                                                            |

| BERRN     | 0                | 37                            | BUS ERROR Output. Active Low, open drain. Asserted by the BPCRT2 Watch-dog timer circuit if UDSN or LDSN are still asserted at the end of the time-out period.                                         |

| CSROMN    | 0                | 54                            | Chip Select ROM Output. Active Low. Asserted by a Read access on the system bus in the ROM address area and when UDSN or/and LDSN are asserted.                                                        |

| CSI/ON    | 0                | 53                            | Chip Select I/O Output. Active Low. Asserted by a Read or Write access on the system bus in the External I/O area, and when UDSN or /and LDSN are asserted.                                            |

| INTN      | ο                | 55                            | Interrupt request output. Active low, open drain. Used to generate interrupts to the CPU.                                                                                                              |

PHILIPS

NOVEMBER ~~ /

1

# BPCRT2-1

### DYNAMIC RAM INTERFACE

| MA0-MA8    | 1/0         | 10-3<br>120              | Memory Address lines. Three state. Multiplexed ROW/COLUMN Address line<br>outputs for DRAM control. Only MA0 to MA7 are significant when 64K DRAMs<br>are used. Least significant bits for Address inputs (A1 to A9) from Coprocessor<br>when CYACK output is asserted. |

|------------|-------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD0-MD15   | <b>I</b> /O | 87-92<br>95-98<br>101-10 | Bidirectional Memory Data bus. Three-state. Also Address and control input during coprocessor cycle.<br>06                                                                                                                                                              |

| RASN       | ο           | 117                      | Row Address Strobe. Active low. Valids the DRAM row address on the falling edge.                                                                                                                                                                                        |

| CAS1-4N    | 1/0         | 116-11                   | 3 Column Address Strobes for memory Bank 1 to 4. Active Low. Valids the DRAM column address on the falling edge. During the reset period, Active High Valids Bank inputs. CAS4 is only used with 64K devices.                                                           |

| CSCGN      | 0           | 109                      | Chip Select Character ROM output. Active low. Used only with the coprocessor interface.                                                                                                                                                                                 |

| UWRN       | 0           | 119                      | Upper Write signal for DRAM. Active low. Is asserted when writing the most significant byte of the DRAM.                                                                                                                                                                |

| LWRN       | 0           | 118                      | Lower Write signal for DRAM. Active low. Is asserted when writing the least significant byte of the DRAM.                                                                                                                                                               |

| DTN        | ο           | 112                      | DATA transfer output. Active low. Used for Video DRAM devices.                                                                                                                                                                                                          |

| CRT CONTRO | OLLER       | INTERF                   |                                                                                                                                                                                                                                                                         |

| P0-P3      | 0           | 73-76                    | Pixel output in 4 bits per pixel mode. Output the 44.SBs of the pixel in 8 bits per pixel mode.                                                                                                                                                                         |

| P4-P7      | 0           | 80-83                    | Output the 4 MSBs of the pixel in 8 bit per pixel mode.                                                                                                                                                                                                                 |

| PCLK       | 0           | 78                       | Pixel Clock. Indicates P0-P7 (or P0-P3) lines are valid on the rising edge.                                                                                                                                                                                             |

| WRPN       | 0           | 72                       | Write Palette output. Active low. Indicates that data available on P0-P7 is control information. Used for an external palette or a Back-end chip.                                                                                                                       |

| VSYNC      | 1/0         | 85                       | Vertical Synchronisation. Active low, Three-state. In Master mode, this output<br>is used as Vertical synchronisation signal for monitor. In Slave TV mode or in<br>Slave Dual mode, becomes a vertical synchronisation Input.                                          |

| HSYNC      | 1/0         | 86                       | Horizontal Synchronization. Active Low, Three-state. In Master mode or Slave TV mode, this output is used as horizontal synchronization signal. In Slave dual mode, it becomes an horizontal synchronisation Input.                                                     |

PHILIPS

PHILIPS Æ

イ

| CSYNCN | Ο | 57 | Composite synchronisation. Active Low, three-state. In Master mode, generates<br>the composite synchronization signal. In Slave TV, generates a symetrical signal<br>which has the horizontal frequency. In Slave Dual mode, generates the phase<br>error between the master and the slave BPCRT2. When display is desabled, this<br>input is used to initialize the synchronization mode. |

|--------|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLANK  | 0 | 84 | Blanking output. Active Low, three-state. Is asserted during vertical and<br>horizontal blanking periods and high the rest of the time except when the Standard<br>EBU is set. In this case and in the 30 MHZ mode, the screen border are in high<br>impedance in order to allow the Standard EBU resolution.                                                                              |

| DA     | 0 | 58 | Display Active output. Active Low, three-state. Is asserted during the vertical retrace period, is in high impedance during the horizontal retrace period, and high the rest of the time.                                                                                                                                                                                                  |

| M/SN   | I | 60 | Master/ Slave input. When high, selects the Master mode.                                                                                                                                                                                                                                                                                                                                   |

### COPROCESSOR INTERFACE

| CYREQN | I | 107 | Cycle Request input from coprocessor. Active low. When asserted, it provokes an information transfer cycle for the coprocessor. |

|--------|---|-----|---------------------------------------------------------------------------------------------------------------------------------|

| CYACKN | 0 | 111 | Cycle Acknowledge output for the coprocessor. Active Low. Is used for Handshake with the coprocessor.                           |

### MISCELLANEOUS SIGNALS

| XTAL1   | I | 123               | Crystal Oscillator Input. Can also be used for External clock Input.                                                                                                                   |

|---------|---|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL2   | ο | 2                 | Crystal Oscillator Output.                                                                                                                                                             |

| RSTINN  |   | 59                | Reset input. Active low. Initiate a reset sequence Internally pulled up.                                                                                                               |

| XT/2    | ο | 122               | Xtal/2 Internal clock output. Frequency is Crystal frequency divided by 2.                                                                                                             |

| XT/4    | 0 | 121               | Xtal/4 Internal clock output. Frequency is Crystal frequency divided by 4.                                                                                                             |

| TST     | I | 61                | Test input. Active high. Must be grounded to VSS in normal condition.                                                                                                                  |

| ΙΡΑ     | I | 56                | Implicit Pixel accelerator Addressing. Active high. It can be used in order to have<br>an implicit addressing of the pixel accelerator in order to increase the<br>manipulation speed. |

| VDD (9) | I | 15-31-4<br>79-93- | 48-62 Power supply pins (5 Volts).<br>•99-108-124                                                                                                                                      |

| VSS (9) | 1 | 1-17-32<br>63-77- | 2-46 Power and signal GROUND pins.<br>94-100-110                                                                                                                                       |

PHILIPS

NOVEMBER 100/

# **BPCRT2-1**

### FUNCTIONS

The BPCRT2 combines in one integrated circuit several functions necessary to implement a basic computer with a 68070 CPU and some memory devices.

The main available functions are:

- -> DISPLAY CONTROLLER with on-chip timing chain, video address generator and shift register logic. A special reload mechanism permits the use of control words dynamically during the display.

- -> SPECIAL DISPLAY FILE DECODER which permits the display of Run-Length coded files and performs the "MOSAIC" effect by using MOSAIC compressed files.

- -> SYSTEM CONTROLLER logic integrating the necessary functions for a minimal system.

- -> DYNAMIC RAM CONTROLLER with direct drive for several types of commonly available devices.

- -> PIXEL MANIPULATION LOGIC optimized for image manipulation under CPU or Coprocessor control.

- -> COPROCESSOR INTERFACE to be used with a high speed dedicated drawing/manipulation peripheral processor. Can also be used to obtain double access memory system.

Electronic components

# PHILIPS

### DISPLAY CONTROL

The BPCRT2 contains the necessary logic to read sequentially the content of a memory area and to serialize it nibble per nibble or byte per byte. The BPCRT2 has a built-in timing generator to assure the generation of the necessary synchronisation signals for the various parts of the chip and for control of the monitor or TV set used as display unit. The device is programmable for several pre-defined modes of display in order to adapt to various applications.

### RESOLUTIONS

BPCRT2 can display images using various modes. These modes are controlled by the DISPLAY COMMAND REGISTER (DCR).

### Horizontal resolution:

The horizontal resolution is set by the following bits of the DCR :

| CF1,CF2 : | CLOCK FREQUENCY, 4 different frequencies are possible.                                     |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| SS :      | SCREEN SIZE, this bit selects either a full size display (SS=1) for over scanned           |  |  |  |  |  |

|           | images or reduced display (SS=0) with an horizontal an vertical programmable color border. |  |  |  |  |  |

| CM :      | COLOR MODE, this bit sets the display to double resolution 4 bits per pixel (CM=1)         |  |  |  |  |  |

|           | or single resolution 8 bits per pixel (CM=0).                                              |  |  |  |  |  |

The following table gives the various possibilities:

| CF1 | CF2 | SS | Frequency | Nb of<br>CM=1 | Px/line<br>CM=0 | Active line |         |

|-----|-----|----|-----------|---------------|-----------------|-------------|---------|

| 0   | 0   | 0  | 19.6608*  | 448           | 224             | 45.6µS      |         |

| 0   | 0   | 1  | 19.6608*  | 512           | 256             | 52µS        |         |

| 0   | 1   | 0  | 24 MHz    | 512           | 256             | 42.6µS      |         |

| 0   | 1   | 1  | 24 MHz    | 640           | 320             | 53.3µS      |         |

| 1   | 0   | 0  | 27.5 MHz  | 640           | 320             | 46.5µS      |         |

| 1   | 0   | 1  | 27.5 MHz  | 720           | 360             | 52.4µS      | TABLE 1 |

| 1   | 1   | 0  | 30 MHz    | 640           | 320             | 42.6µS      |         |

| 1   | 1   | 1  | 30 MHz    | 768 +         | 384+            | 51.2µS      |         |

#### NOTES:

\* This frequency is used by the 68070 and allows for a single frequency minimal system.

+ The number of visible pixels can be reduced to 360 or 720 by utilizing the BLANKN signal to reduce the visible line to 48 μS (see VIDEO SYNCHRONIZATION).

-->If the NORMAL mode is used for DRAM access, only the 4-bits/pxl mode is available and the resolution is In half.

PHILIPS

-->In Double frequency mode (SM=0,DF=1), the line period and the horizontal resolution are divided by 2. This mode does not exist with CF1=CF2=0.

-->When using Dual Port Video Ram with external shift registers, it is possible to increase the resolution.

Electronic components

NOVEMBER

4

### Vertical resolution:

0

1

1

SWSXPACE OF CONTRACTOR

The vertical resolution is set by the following bits in the DCR are :

- FD : FRAME DURATION, this bit selects a 50 or a 60 Hz scan frequency (assuming the CF1-2 bits are set to an allowed crystal frequency in table 1). A zero forces a 50 Hz scan (312 or 625 lines per frame). When FD is set to 1, the scan becomes 60 Hz compatible (262 or 525 lines).

- SS: SCREEN SIZE, as for the horizontal size, this bit has an effect on the vertical size of the active screen. If set to 1, the display will be compatible with a full screen display like TV image. When SS bit is reset to 0, the display becomes reduced with a top and a bottom border of the programmable color.

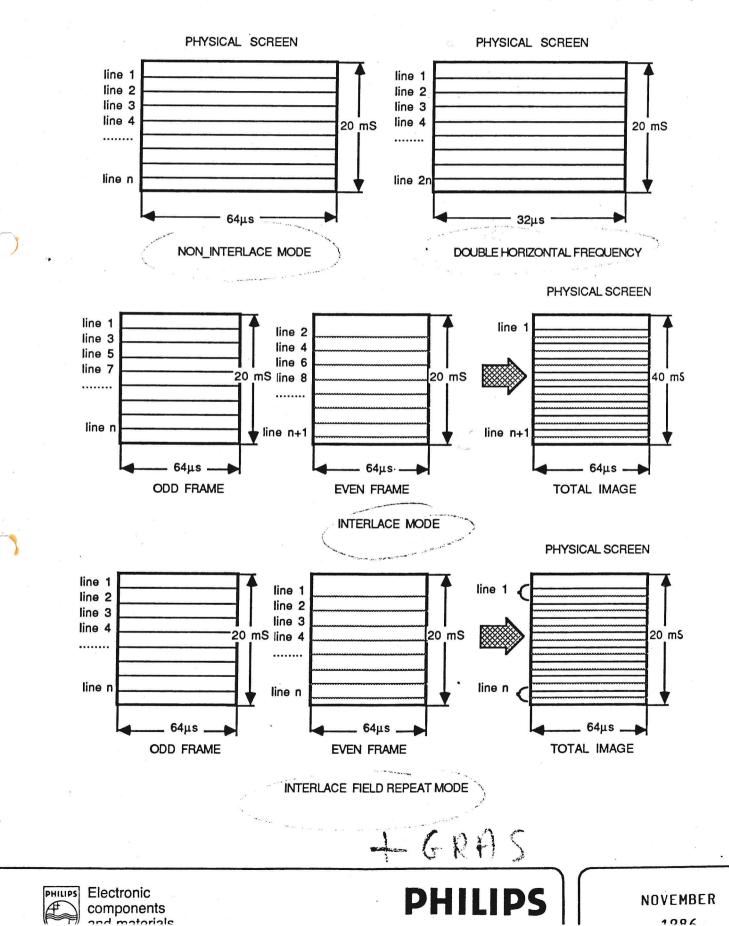

- SM . DF : These 2 bits permit the use of 4 different scan modes as indicated as follows :

- SM DF SCAN MODE

- 0 0 Non-interlace mode.

- 1 Non-interlace mode with a double horizontal frequency. The vertical frequency is the same, this doubles the vertical resolution. Not usable with CF1=CF2=0

- 0 Interlace mode. 2 interleaved frames are generated, the odd frame displays the odd memory lines and the even frame displays the even memory lines. At the end of the memory line N display, there is an automatic jump to the memory line N+2. The displayed memory size is 2 times bigger than in the non-interlace mode.

- 1 Interlace field repeat mode. This interlace mode has 2 interleaved frames displaying the same memory field. The displayed memory size is the same as in non-interlace mode. This permits synchronization with the TV standard.

PHILIPS

The following table summarizes the various possibilities:

| FD  | SS | SM | DF | Nb of lines | Frame Duration | Image F | requency |

|-----|----|----|----|-------------|----------------|---------|----------|

| 0   | 0  | 0  | 0  | 250         | 16mS           | 50Hz    |          |

| 0   | 0  | 0  | 1  | 500         | 16mS           | 50Hz    |          |

| 0   | 0  | 1  | 0  | 500         | 16mS (x2)      | 25Hz    |          |

| 0   | 0  | 1  | 1  | 250         | 16mS (x2)      | 50Hz    |          |

| 0   | 1  | 0  | 0  | 280         | 18mS           | 50Hz    |          |

| 0   | 1  | 0  | 1  | 560         | 18mS           | 50Hz    |          |

| 0   | 1  | 1  | 0  | 560         | 18mS (x2)      | 25Hz    |          |

| 0   | 1  | 1  | 1  | 280         | 18mS (x2)      | 50Hz    |          |

| 1   | 0  | 0  | 0  | 210         | 13.4mS         | 60Hz    | TABLE 2  |

| 1   | 0  | 0  | 1  | 420         | 13.4mS         | 60Hz    |          |

| 1   | 0  | 1  | 0  | 420         | 13.4mS (x2)    | 30Hz    |          |

| 1   | 0  | 1  | 1  | 210         | 13.4mS (x2)    | 60Hz    |          |

| . 1 | 1  | 0  | 0  | 240         | 15.3mS .       | 60Hz    |          |

| 1   | 1  | 0  | 1  | 480         | 15.3mS         | 60Hz    |          |

| 1   | 1  | 1  | 0  | 480         | 15.3mS (x2)    | 30Hz    |          |

| 1   | 1  | 1  | 1  | 240         | 15.3mS (x2)    | 60Hz    |          |

# **BPCRT2-1**

## **BPCRT2-1**

#### **DISPLAY MODES**

#### Reduced and full screen

Two modes are available mainly intended either for TV applications where an over-scanned picture is used or for text applications where it is necessary to see the total active screen. The first mode is named Full-Screen mode (SS=1) and the second mode is named Reduced Screen mode (SS=0). In Reduced Screen mode, a border of programmable color is displayed on the top, bottom, left and right parts of the visible screen. The BORDER REGISTER is 8 bits wide allowing for 256 colors in 8 bits per pixel mode or for 16 colors in 4 bits per pixel mode. In this case, only the 4 MSBs are used (BORDER[7:4]).

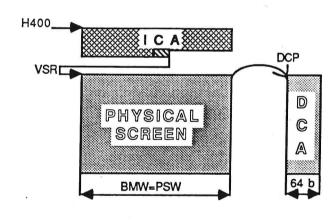

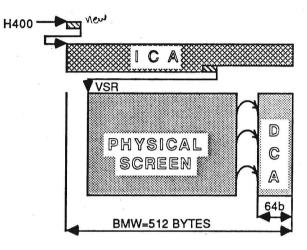

### Physical and logical screen

Independently of that, two types of memory arrangements are available. The simple case is named Physical Screen mode; it corresponds to a direct representation of an area in memory where the first pixel of a line is placed immediately after the last pixel of the previous line. The other, named Logical Screen mode uses a fixed length of a line in memory which is longer than the visible line. It allows rolling of the display horizontally.

The bit LS of the DCR is used to set one of these 2 modes.

At the beginning of each frame the VIDEO START ADDRESS REGISTER (VSR) points to the first pixel of the first video line to be displayed. The pixels to be displayed at the other video lines depend on the type of screen.

--> In **Physical Screen** mode (LS=0), the first pixel address of the current video line (fpacl) is just after the last pixel address of the previous line (lpapl), that means: fpacl=lpapl+1.

When the scan mode is interlaced (SM=1,DF=0), fpacl=lpapl+1+1line.

When the Interleaved Dynamic Control Area DCA (see next chapter) is set, fpacl=lpapl+1+DCAsize.

When the interleaved DCA and interlace mode are set, fpacl=lpapl+1+1line+DCAsize.

It is not possible to use the reduced DCA mode and the interlace mode simultaneously. The physical screen mode permits to optimize the memory area and avoid refresh cycle during the display area. When using subscreens by reloading the VSR register, one of 2 consecutives subscreens must have at least 4 lines to insure the memory refresh. In the 27.5 Mhz mode and in full screen mode, the Physical Screen width is 768 pixels even if the resolution is 720 pixels in 4 bits per pixel mode (respectively 384 and 360 pixels in the 8 bits per pixel mode).

--> In Logical Screen mode (LS=1), the video lines (in memory) start at an address multiple of 128 long words. The physical display starts at the value of the Video Start Address register and ends after the programmed number of pixels per video line.

To fetch the first pixel of the current line, the LSBs of the Video Start Address register are reloaded into the counter and the MSB are incremented of 128 longwords. Thus fpacl=fpapl+128longword. The width of the logical screen is equal to 512 bytes independently of the resolution chosen, so giving an area of 1024 pixels in 4bits/pxl mode or 512 pixels in 8bits/pxl mode. The displayed memory area

PHILIPS

NOVEMBER

is always less than 512 bytes, this gives the possibility of horizontal rolling. UVRNPAROUN

FIGURE 4: PHYSICAL and LOGICAL MODE

| PHYSICAL SCREEN MODE | LOGICAL SCREEN MODE |

|----------------------|---------------------|

| BMW=PSW*             | BMW=512bytes        |

| PHYSICAL<br>SCREEN   | PHYSICAL            |

\* BMW=Bit Map Width

PSW= Physical screen Width

Electronic components and materials

**BPCRT2-1**

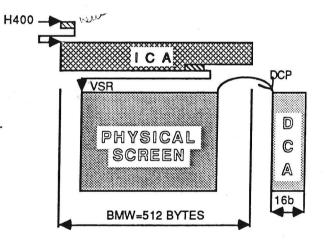

### IMAGE CONTROL AREA (ICA) and DYNAMIC CONTROL AREA (DCA) MECHANISMS

The BPCRT2 offers the possibility to fetch control information during horizontal and vertical retrace periods in order to change the contents of internal registers, to control a Back-end processor (BEP) or to generate an interrupt. Two bits are used to control these mechanisms (IC and DC).

#### ICA mechanism

The image control area (ICA) mechanism consists of fetching instructions during the vertical retrace period. In the begining of the vertical retrace period, BPCRT2 fetches the first ICA instruction at the location H400. or H80400 (see DRAM DESELECT) which is the beginning of the ICA. The ICA instructions can be passed to the BEP or used internally to reload the border color register or the video start address (VSR) or drive the interrupt pin. When an ICA STOP instruction is decoded, the VSR is reloaded for display and the BPCRT2 waits for the beginning of the active display area.

The size of the ICA can be large because the ICA fetches take place during the non-dispayed lines of the vertical retrace. This mechanism allows for reload of a 256 entry Colour Look-up Table (CLUT) in the BEP and complete update of the mode of the system during one frame retrace. The instruction "reload VSR" permits an indirect addressing which can be used to place the ICA anywhere in the first megabyte of memory.

#### DCA mechanism

The dynamic control area (DCA) mechanism has the same concept as the ICA mechanism but it is performed at the end of each video line, allowing dynamic control during an image display. The DCA is fetched immediately after the end of the active display line and not during the vertical retrace. The DCA has the same type of instructions as the ICA. The memory allocation for the DCA depends on which mode is set by the ID bit of the DCR2 register: The interleaved DCA mode (ID=0)

The independant DCA mode (ID=1)

#### Interleaved DCA mode

In Physical Screen mode, the DCA is placed between the end of the physical line and the beginning of the next line. The size of the DCA is either 16 Bytes (reduced DCA) or 64 Bytes.

In Logical Screen mode, the DCA is placed in the last part of the logical line. When the physical video line is fetched, the LSBs of the long word address are forced to 1F0 (reduced DCA) or 1C0 in order to fetch the first control word of the DCA. It is then incremented normally. The logical screen is wrapped between the long word just before the DCA and the first location of the line so the DCA will never be fetched as active display area if the VSR never points to the DCA area.

#### Independant DCA mode

For this mode the DCA is an independant bitmap which is 16 bytes (reduced DCA) or 64 bytes wide. The first line is pointed to by a dedicated DCA POINTER, DCP, which is different from the VSR register that points to the display area and the ICA. DCP is longword aligned. The DCA of the second line is automatically pointed to by DCP+16 bytes (reduced DCA) or by DCP+64 bytes. As for the VSR register, it is possible to change the content of the DCP register during the display in order to use a different independant DCA bitmap.

In Physical Screen mode, the DCA size is not added to the physical line, the displayed memory lines are always adjacent.

In Logical Screen mode, the logical screen is entirely dedicated for the display. The Logical line is wrapped between the first pixel and the last pixel of the line. It is therefore easier to perform horizontal rolling.

Electronic components

### Page n° 12

## **BPCRT2-1**

### FIGURE 5: ICA and DCA examples

PHYSICAL SCREEN MODE WITH ICA AND INTERLEAVED DCA

H400 VSR PHYSICAL C SCREEN A BMW=PSW+64

PHYSICAL SCREEN MODE WITH ICA AND INDEPENDANT DCA

\* BMW=Bit Map Width PSW= Physical screen Width LOGICAL SCREEN MODE WITH ICA AND INTERLEAVED DCA WITH INDIRECT ADDRESSING OF THE ICA

LOGICAL SCREEN MODE ICA WITH INDIRECT ADDRESSING OF THE ICA, INDEPENDANT AND REDUCED DCA

RELOAD VSR and STOP" INSTRUCTION

#### DCA and ICA initialization

The control areas are set using the IC and DC bits of the DCR register. There are then four possible modes:

DHI

| IC | DC | ICA | DCA  | TABLE 3                              |

|----|----|-----|------|--------------------------------------|

| 0  | 0  | no  | no   |                                      |

| 0  | 1  | yes |      | REDUCED DCA MODE DCA size = 16 bytes |

| 1  | 0  | yes | no   |                                      |

| 1  | 1  | yes | yes> | DCA size = 64 bytes                  |

Electronic components

### **BPCRT2-1**

When IC=DC=1, the number of possible fetches in the DCA can be limited by the line retrace duration. The following table indicates the different possibilities :

| IA               | BLE 4: |     |     |              |

|------------------|--------|-----|-----|--------------|

| DOUBLE FREQUENCY | SS     | CF1 | CF2 | DCA in bytes |

| (SM=0,DF=1)      |        |     |     | 5.2 A        |

| 0                | 0      | 0   | 0   | 64           |

| 0                | 1      | 0   | Х   | 32           |

| 0                | 1      | 1   | 0   | 32           |

| 0                | 1      | 1   | 1   | 64           |

| 1                | X      | х   | X   | 16           |

|                  |        |     |     |              |

When the effective DCA is longer than indicated, an automatic STOP is performed. The allocated memory size for the DCA is always 64 (IC=DC=1) or 16 bytes (IC=0,DC=1) even if the effective DCA size is shorte) fr. In SLOW mode (for the DRAM), the possible DCA fetches are divided by 2.

### **ICA and DCA instructions**

An instruction is 32 bit wide and longword aligned, so always pairs of words will be fetched. The content of the MSBs of those long words give the operation to be performed. 9 different instructions are possible :

| TABLE 5:                |                                                                                                                                                  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000                    | STOP. Stop the control sequence. The instructions fetches are then                                                                               |

|                         | stopped for the rest of the line concerning the DCA or until the beginning of the active display area concerning the ICA.                        |

| 0001                    | NOP. No operation.                                                                                                                               |

| 0010 PPPP               | RELOAD DCP. Reload the DCP and its associated address counter                                                                                    |

| PPPP PPPP PPPP PPPP     | with the specified pointer. The next fetches will use the new value.<br>This permits an indirect addressing for the independant DCA mechanism.   |

| 0011 PPPP               | RELOAD DCP and STOP. Reload the DCP with the specified pointer,                                                                                  |

| PPPP PPPP PPPP PPPP     | then stop control fetches as with the STOP instruction.                                                                                          |

|                         |                                                                                                                                                  |

| .0100 PPPP              | RELOAD VSR. Reload the VSR and the video address counter with the specified                                                                      |

| PPPP PPPP PPPP PPPP     | pointer. The next fetches will use the new value. This permits the use of subscreens or indirect addressing for the ICA and the interleaved DCA. |

| 0100 PPPP               | RELOAD VSR and STOP. Reload the VSR with the specified pointer,                                                                                  |

| PPPP PPPP PPPP PPPP     | then stop the control fetches as with the STOP instruction.                                                                                      |

|                         |                                                                                                                                                  |

| 0110                    | INTERRUPT. Generate an interrupt to the CPU.                                                                                                     |

|                         |                                                                                                                                                  |

|                         |                                                                                                                                                  |

| 0111 CCCC CCCC          | RELOAD BORDER. Reload immediately the border color register with the                                                                             |

|                         | specified color.                                                                                                                                 |

|                         |                                                                                                                                                  |

| 1XXX XXXX XXXX XXXX     | BEP CONTROL. Control of the Back-End processor. (see BEP interface). The                                                                         |

| XXXXX XXXXX XXXXX XXXXX | WRPN signal goes low and the 32 bits are passed to the BEP without alteration.                                                                   |

PHILIPS

PHILIPS Æ

いたがいたい あいちがい たまたい いいたい いたい

Electronic components

### **BPCRT2-1**

#### SCREEN MANAGEMENT

When the IC and DC bits are equal to zero (no Control Area), the start address of the screen must be loaded by the CPU in the video start register VSR before activation of the display controller. This register is 20 bits wide, so the screen start can be located anywhere in the first Mbyte of RAM(H0 to H100000).

### Horizontal and vertical rolling

Because of the DRAM interface used, the beginning of each line is long word aligned. In logical screen mode, a horizontal offset can be introduced to allow for horizontal soft rolling pixel per pixel in 8 bits/pxl mode or 2 pixels per 2 pixels in 4bits/ pxl mode. In order to specify the offset to start with, 2 bits are added acting as LSBs of start address to define a byte address. Those bits are placed in the VSR as 00 and 01 locations, resulting in a 20-bit byte address pointing to an area in DRAM.

The ability to change the VSR value for the beginning of the frame allows vertical rolling line per line from one frame to the next one. The CPU will have to reload the VSR with current address plus or minus the width of the bitmap.

By reloading the VSR dynamically, the ICA and DCA mechanism make the horizontal and vertical rolling easier.

#### Subscreens

The reloading of VSR effects a "jump" from one memory location to another. This allows the display of several subscreens, each of them being built from a different memory area. Changing the various new VSR values in the DCAs will generate rolling or scrolling inside each subscreen independently.

#### **PIXELS OUTPUT**

The BPCRT2 gives two possible modes of pixel output by serializing the memory contents in two ways. The 16-bit words are divided either in 2 bytes to be serialized via 8 outputs (P0 to P7) or in four nibbles to be serialized via 4 outputs (P0-P3). The correspondance between displayed memory word and pixel is as follows:

| In 4 bits per pixel: | P0 = D15>D11-<br>P2 = D13>D9 |             | P1 = D14>D10>D6>D2<br>P3 = D12>D8>D4>D0 |             |  |

|----------------------|------------------------------|-------------|-----------------------------------------|-------------|--|

| In 8 bits per pixel: | P0 = D15>D7                  | P1 = D14>D6 | P2 = D13>D5                             | P3 = D12>D4 |  |

|                      | P4 = D11>D3                  | P5 = D10>D2 | P6 = D9>D1                              | P7 = D8>D0  |  |

The output of the pixel content is clocked by the Pixel Clock signal (PCLK). In 4bits/pxl mode, the PCLK frequency is the XTAL frequency divided by 2 (max: 15 MHz), in 8bits/pxl mode it is XTAL frequency divided by 4 (max: 7.5MHz). On rising edges of PCLK, the data presented on P0-P7 (or P0-P3) is valid.

When the 4bits/pxl mode is selected, the P4 to P7 outputs are zeroed.

During the blanking period, the pixel content will be zero (if DC=0).

During the display period, the BPCRT2 transfers to the pixel output, the bytes (or nibbles) in a transparent way (no interpretation of the contents). It is possible to add a Back-End Processor which can perform additionnal pixel processing before transmission to the monitor.

When used without a Back-End processor, the BPCRT2 can generate 4 or 8 bits for a resistor network or a set of three D/A converters.

PHILIP

NOVEMBER

Electronic components

「「「「「「「「「「「「」」」」」」」」」

**BPCRT2-1**

### BACK-END PROCESSOR (BEP) INTERFACE

During the Horizontal retrace periods (including vertical retrace), the BPCRT2 can generate control signals for the BACK-END Processor if the Image Control or Dynamic Control Mode (IC or DC bit) are selected. The Write palette signal (WRPN) is asserted to indicate that the DATA available on P0-P7 (even in 4-bit mode) is not a pixel content but a value to be loaded into the Back-End Processor. This information is composed of a serie of up to 16 Longwords (64 transfers) coming from an area written in memory by the CPU or Coprocessor. The various DC1 registers of the Back-End Processor can be reloaded before each video line using this mode.

The information will be sent to the Back-End Processor in groups of 4 bytes. The BPCRT2 will test the MSB (MD15) of the first word. If this bit is equal to one the transfer to the BACK-END processor will occcur. If MD12 to MD15 are zeroed, it will disable the control mode for the rest of the current video line. So it is possible to grant the remaining accesses to the coprocessor or to the system bus. Note that if the DC bit is set and if no control information is necessary for the current line, the user must reset the four MSBs of the first word of the DCA.

When the Reduced screen mode is performed, the border color is immediately sent to the back-end processor after the display active area. If the WRP signal is asserted when BLANK is still high, the BEP must hold the border color during the control sequence.

The BEP must stop the generation of the border color during the Blanking period.

The following diagrams give the various sequences which can occur at the end of the active display lines:

| 8 bits/j     | bixel full screen mode :                            |

|--------------|-----------------------------------------------------|

|              | -displayretrace                                     |

| BLANKN       |                                                     |

| WRPN         |                                                     |

| P0-P7        |                                                     |

|              | last pixels control bytes from DCA STOP instruction |

| PCLK         |                                                     |

| 4 bits/pi    | xel reduced screen mode :                           |

|              | display ——right border ——retrace ——retrace ——       |

| BLANKN       |                                                     |

| WRPN         |                                                     |

| P0-P3        |                                                     |

| las<br>P4-P7 | control bytes from DCA STOP instruction             |

| PCLK         |                                                     |

PHILIPS

FIGURE 6: BEP INTERFACE

Electronic components

### **BPCRT2-1**

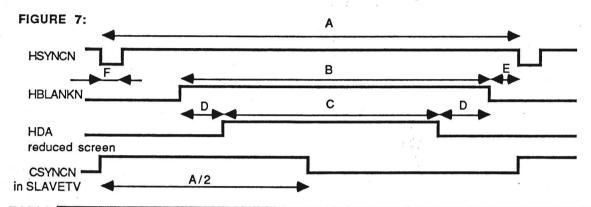

### VIDEO SYNCHRONIZATION

The BPCRT2 generates signals for synchronization of a TV set or a monitor. Furthermore, the synchronization signals are programmable to be a master, a slave to another BPCRT2 (DUAL MODE) or slave to incoming TV Synchronization signals. The status of the MASTER/SLAVE and the GSYNC-pins (when the DE bit of the DCR = 0) are used to set the synchronization mode as follows :

| M/SN | CSYNCN pin<br>DE=0 | SYNCHRO MODE |

|------|--------------------|--------------|

| 1    | x                  | MASTER       |

| 0    | 1                  | SLAVE TV     |

| 0    | 0                  | SLAVE DUAL   |

When DE = 0 (display disable), the CSYNCN pin is an input so that the SYNCHRO MODE can be initialized. A pull up resistor being internally connected to the CSYNCN pin, so the initialization of the slave TV mode does not need any pull-up resistor but a pull down resistor is necessary to initialize the slave dual mode. When DE is set to 1, the CSYNCN state is latched and CSYNCN becomes an output pin.

If DE is zeroed the chip is in the display off mode, the synchro signals and the pixel output are in the high impedance state. The DRAM bus interface is still available for system and coprocessor accesses. DRAM access is not synchronized on video fetches anymore but are resynchronized on a host or coprocessor access to give a shorter reaction time and a better transparency for the host and/or coprocessor access. The DE bit is reset by the RESET sequence, and when it is set to 1, the synchro pins are used as follows:

In MASTER mode, HSYNCN, CSYNCN and VSYNCN signals are generated.

In SLAVE TV mode, HSYNCN is generated, the VSYNCN pin is in input mode and must receive an external VSYNC signal, the CSYNCN pin is used to output a signal which has the HSYNCN period but with a duty cycle = 1 to input into the phase comparator of an external phase-locked-loop oscillator. This signal is high during the first half of each line.

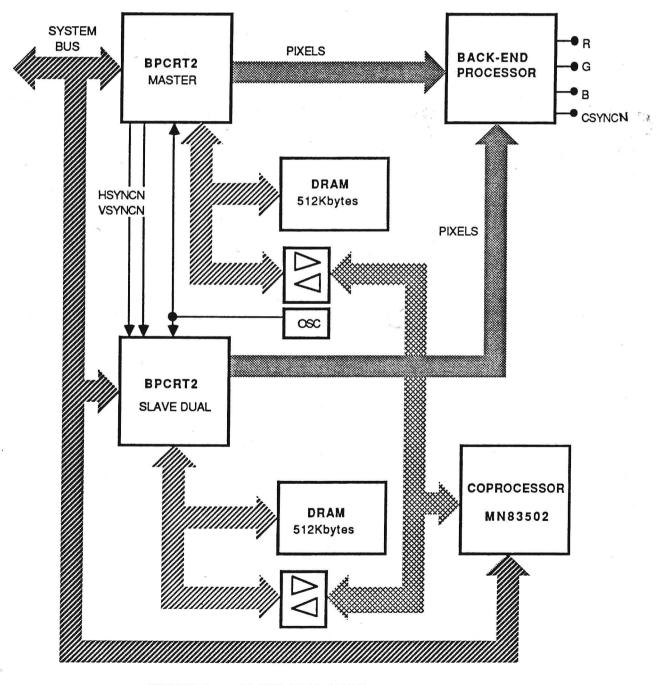

In SLAVEDUAL mode, HSYNCN and VSYNCN pin are in Input mode and have to receive external HSYNC and VSYNCN. CSYNCN generates the phase error between the internal and the external HSYNCN signal. This mode is used when more than one BPCRT2 are needed to increase the pixel depth, one is in MASTER or SLAVE TV mode, the others in SLAVEDUAL mode and receiving the synchro signals from the MASTER BPCRT2.

The BLANKN information is active low during non display periods. The pin is driven high during the active display period. In the 30 MHz mode when the ST bit of the CSR is high, the BLANKN signal is in high impedance during the 12 first and 12 last pixels of the line in 8bits/pxl mode (24 pixels in 4bits/pxl mode). The Back-End Processor can thus display 384 or 360 pixels of 8 bits (768 or 720 pixels of 4 bits) with a pull-up or a pull-down resistor on the BLANKN pin.

The DA pin generates the Display Active signal which is low during the vertical retrace, high during the display line and high impedance during the line retrace. With a pull-up or pull-down resistor it is possible to disable or enable, respectively, the horizontal component of DA.

PHILIPS

NOVEMBER

PHILIPS

Electronic components

FIGURE 7 and TABLE 6 represent the horizontal timing with HSYNCN and the horizontal components of BLANKN and DA signal in Reduced screen mode. The timings available in the chart are given as an equivalent number of pixels per line when the 4 bits/pixel mode is used. It has to be divided by two in 8 bits/pixel mode and in DOUBLE FREQUENCY modes.

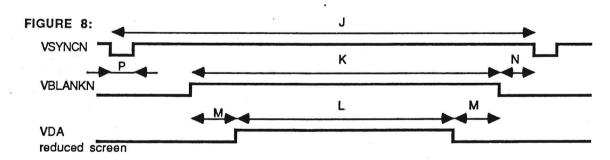

FIGURE 8 and TABLE 7 represent the vertical timing with VSYNCN and the vertical components of BLANKN and DA signal in Reduced screen mode. The timings given assume one line= $64\mu$ S. In DOUBLE FREQUENCY mode the vertical timing is the same as in the non-interlace mode.

| TABLE | 19.6608 | 3 Mhz | 24     | Mhz   | 27.5   | Mhz   | 30     | Mhz   |

|-------|---------|-------|--------|-------|--------|-------|--------|-------|

| 6     | Pixels  | μS    | Pixels | μS    | Pixels | μS    | Pixels | μS    |

| A     | 640     | 65.1  | 768    | 64    | 880    | 64    | 960    | 64    |

| В     | 512     | 52.08 | 640    | 53.33 | 720    | 52.36 | 768    | 51.2  |

| С     | 448     | 45.57 | 512    | 42.67 | 640    | 46.55 | 640    | 42.67 |

| D     | 32      | 3.26  | 64     | 5.33  | 40     | 2.91  | 64     | 4.27  |

| E     | 16      | 1.63  | 8      | 0.67  | 16     | 1.16  | 24     | 1.6   |

| F     | 48      | 4.88  | 56     | 4.67  | 64     | 4.65  | 72     | 4.8   |

| G     | 24      | 2.44  | 24     | 2     | 32     | 2.33  | 32     | 2.13  |

| Н     | 48      | 4.88  | 56     | 4.67  | 64 🛁   | 4.65  | 72     | 4.8   |

| TABLE | 50 Hz r | non-interlace | 50 Hz ir | nterlace | 60 Hz n | on-interlace | 60 Hz ir | nterlace |

|-------|---------|---------------|----------|----------|---------|--------------|----------|----------|

| 7     | lines   | mS            | lines    | mS       | lines   | mS           | lines    | mS       |

| J     | 312     | 19.97         | 312.5    | 20       | 262 .   | 16.77        | 262.5    | 16.8     |

| К     | 280     | 17.92         | 280      | 17.92    | 240     | 15.36        | 240      | 15.36    |

| L     | 250     | 16            | 250      | 16       | 210     | 13.44        | 210      | 13.44    |

| М     | 15      | 0.96 .        | 15       | 0.96     | 15      | 0.96         | 15       | 0.96     |

| Ν     | 6       | 0.384         | 6 or 6.5 | 0.416    | 4       | 0.256        | 4 or 4.5 | 0.288    |

| Р     | 2.5     | 0.16          | 2.5      | 0.16     | 3       | 0.192        | 3        | 0.192    |

PHILIPS

Electronic components

「「「ない」のないです。ここではないです。

**BPCRT2-1**

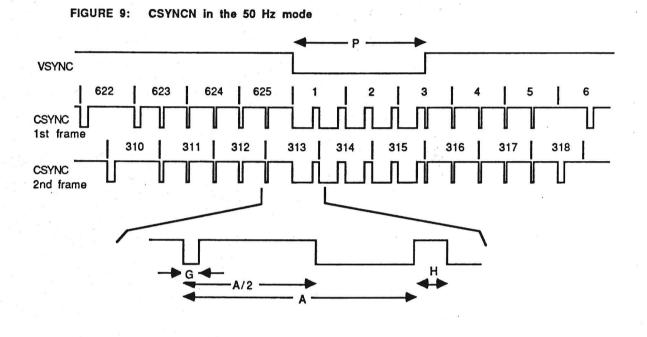

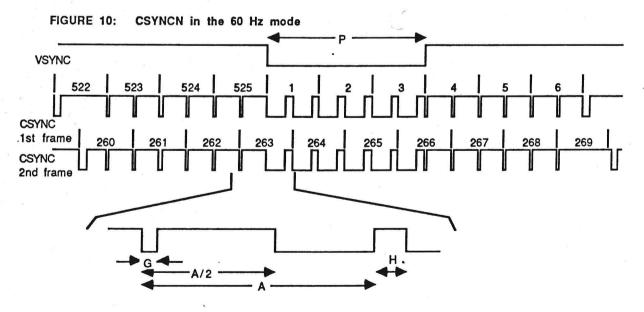

FIGURE 9 and 10 represent the CSYNCN signal when BPCRT2 is in MASTER mode and interlace mode (SM=1). The 50Hz mode is shown in figure 9 and the 60Hz mode is shown in figure 10.

PHIL

PHILIPS

Electronic components

### **BPCRT2-1**

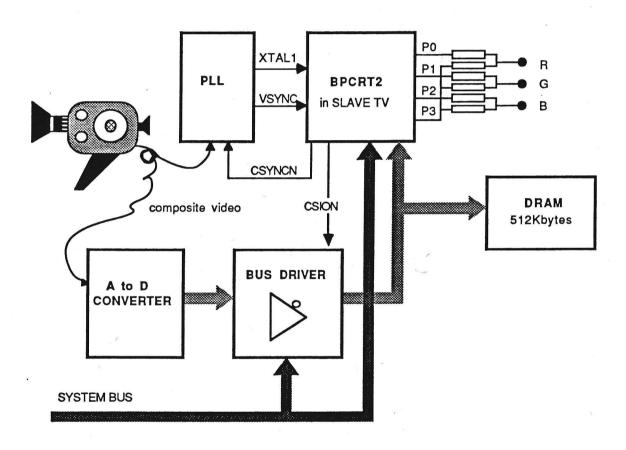

### FRAME GRABBING

The BPCRT2 can be synchronized on an incoming TV signal, which makes it possible (with a small amount of external circuits), to "grab" the image information and load it into the memory. When the FRAME-GRABBING bit FG is set, the BPCRT2 will end the current frame (two fields eventually) and start the grabbing period which is one or two frames long depending on the scanning mode.

During the grabbing period, the display scanning remains exactly the same but the UWRN and LWRN signals to the memory are asserted during the normal display active period. The external hardware must place the results of the A/D conversions for each pixel on the DATA bus, synchronously with the access to the memory. The memory will thus load the new picture and the BPCRT2 will display it as normal.

CPU or coprocessor memory access is not granted during the grabbing. The BERR generator is also disabled during the grabbing period. The internal registers are always accessible.

At the end of the frame grabbing, the FG bit is reset by BPCRT2 automatically and the previous mode is performed. During the grabbing the FG bit is readable in the command status register CSR.

The device is able to grab in real time, on-the-fly, TV images with a resolution of 768x560 pixels of 4 bits or 384x280 pixels of 8 bits.

FIGURE 11 shows a grabbing period in the interlace mode. During the 2 frames, the DRAM access is disabled and the DRAM write signals are asserted:

| VSYNC                    |                       | Л                   |

|--------------------------|-----------------------|---------------------|

| FG                       |                       | 1                   |

| disable *<br>DRAM access |                       | jan<br>Line<br>Line |

| UWRN<br>LWRN             | vertical retrace      |                     |

|                          | DA width line retrace | х.<br>              |

FIGURE 11: FRAME GRABBING

\* internal signal

Electronic components

# PHILIPS

# **BPCRT2-1**

### **DISPLAY FILES**

「「ないない」となった。こので、これになっていた。

BPCRT2 can handle 3 types of file :

- --> NORMAL file: organized as a bit map where each pixel has its own address

- > RUN-LENGTH file: consecutive pixels with the same color are grouped in the same block of information

- --> MOSAIC file: as normal file but with resolution divided by a MOSAIC factor, the BPCRT2 is responsible for duplicating each pixel following the MOSAIC factor (2, 4, 8 or 16).

The 2 last types of files permit information compression to save space in the storage system, they are well adapted to achieve fast speed loading and animation.

The initialization of the file type is made with the FT1-2 bits of the DCR2 registers :

| FT1 | FT2 |             |

|-----|-----|-------------|

| 0   | X   | NORMAL file |

| 1   | 0   | R-L file    |

| 1   | 1   | MOSAIC file |

#### **RUN LENGTH**

The RUN-LENGTH coding technique permits file compression by grouping in one block consecutive pixels which have the same color. The compression factor can be very important, for instance a screen which has a uniform colour needs a very short memory space in a RUN-LENGTH format. The RUN-LENGTH compression is applied to each video line independently of the others.

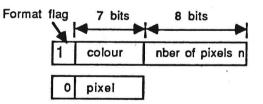

The RUN-LENGTH file is organized as a list of information about pixels without notion of width and height as in bit map files. The information indicates either the pixel colour followed by the number of consecutive pixels having the same colour, or the simple pixel. Thus, 2 formats are possible :

#### FIGURE 12:

The MSB indicates if the information is on 2 bytes (consecutive pixels having the same colour) or on 1 byte (pixel alone). The number of colours in 8 bits/pixel mode is therefore limited to 128. The number of consecutive pixels, n, is between 2 and 256. When n = 0, the display controller of BPCRT2 finishes the display line with the last indicated colour. Each line has to be finished with n = 0. <u>example</u>:

| Display | = Line 1<br>Line 2 |      |        |       |        |      |        |       | red<br>pink |  |  |

|---------|--------------------|------|--------|-------|--------|------|--------|-------|-------------|--|--|

| File =  | blue 2             | cyan | grey : | 3 red | 2 gree | en O | pink 5 | black | pink 0      |  |  |

PHILID

NOVEMBER

Electronic components

### **BPCRT2-1**

In 4 bits/pixel mode, it is also possible to use the RUN-LENGTH technique. As BPCRT2 processes RUN-LENGTH files at the byte level, the RUN-LENGTH decoding works by groups of 2 pixels, each pixel being limited to 8 colours in order to use the MSB as a format flag. This format flag is output with the pixel of 3 bits via the pixel output port (P0-->P3).

example :

8 bits |<---->| 1 blue pink pink pink pink pink -> end of live Display = red red red red blue blue File = (red red) 2 (blue blue) (blue pink) (pink pink) 0

### MOSAIC

The MOSAIC technique consists of changing the resolution of the screen by duplicating pixels and lines by a MOSAIC factor.

The effect on the screen is a granulation. The MOSAIC file can be compressed by a factor n x m where n is the horizontal MOSAIC factor and m the vertical MOSAIC factor.

Depending on the horizontal MOSAIC factor, BPCRT2 duplicates automatically the pixel on the line (horizontal MOSAIC). The MOSAIC factor is indicated into the DCR2 register :

| MF1 | MF2 | MOSAIC FACTOR |

|-----|-----|---------------|

| 0   | 0   | 2             |

| 0   | 1   | 4             |

| 1   | 0   | 8             |

| 1   | . 1 | 16            |

example with horizontal MOSAIC factor = 2 and normal resolution = 10 pixels/line :

MOSAIC file = Green blue red orange brown yellow ...

screen = line n°1 : Green green blue blue red red orange orange brown brown line n°2: Yellow Yellow....

Concerning the vertical MOSAIC, the independant DCA can be used to duplicate the lines. The vertical MOSAIC can therefore be independent of the horizontal MOSAIC factor.

### DCA AND INTERLACE MODE FOR RUN-LENGTH AND MOSAIC FILES

The video start register VSR is used to point at the beginning of lines as for the normal type of file. When using the DCA mechanism, only the independant DCA can be used, The where of physical and logical score descent the interlace mode is not usable with RUN-LENGTH and MOSAIC files but it is possible to obtain the interlace effect with RUN-LENGTH files by using the interlace field repeat mode. In this case the VSR has to be changed at the end of each frame. The parity bit of the CSR status register indicates the frame parity for the interlace and interlace repeat mode. This bit permits synchronization of the reload of VSR with the 2 frames.

Electronic components

# **BPCRT2-1**

### SYSTEM CONTROL

The BPCRT2 performs several system oriented control functions which are always necessary in a minimal system. The address decode, the access arbitration between various masters of the DRAM bus and the Reset timing generation are some of them. The following paragraphs will describe in detail the various functions.

### ADDRESS DECODING

The BPCRT2 is connected to the system bus via 20 Address lines, giving 2 Megabytes of addressing range, the control bus (CSN, UDSN, LDSN, R/WN, DTACKN, BERRN, HALTN, RSTOUTN) and the 16-bit DATA bus. The chip controls the access to the resources of a minimal system i.e. 1.5MByte of DRAM, 0.5 MByte of ROM and internal registers and external I/O devices.

The system bus interface is 68000 compatible and is enabled when CSN is low and either UDSN or LDSN are asserted. The mapping depends on the type of DRAM which is used (256K or 64K) and on the synchro mode as indicated in this BPCRT2 mapping table :

| TABLE 8                      | 256                   | к             | 64 K                  |               |  |

|------------------------------|-----------------------|---------------|-----------------------|---------------|--|

| ADDRESS                      | MASTER<br>OR SLAVE TV | SLAVE DUAL    | MASTER<br>OR SLAVE TV | SLAVE DUAL    |  |

| 0 0 0 0 0 0<br>0 1 F F F F   | 1                     |               | BANK 1                |               |  |

| 020000<br>03FFFF             | DANICA                | DANK (        | BANK 2                |               |  |

| 040000<br>05FFFF             | BANK 1                | BANK 1        | BANK 3                |               |  |

| 0 6 0 0 0 0<br>0 7 F F F F   |                       |               | BANK 4                |               |  |

| 080000<br>09FFFF             |                       |               |                       | BANK 1        |  |

| 0 A 0 0 0 0<br>0 B F F F F   | BANK 2                | BANK 2        |                       | BANK 2        |  |

| 0 C 0 0 0 0<br>0 D F F F F   | DANK 2                | DAINK 2       |                       | BANK 3        |  |

| 0 E 0 0 0 0<br>0 F F F F F   | -                     |               |                       | BANK 4        |  |

| 1 0 0 0 0 0<br>1 7 F F F F   | BANK 3                | BANK 3        |                       |               |  |

| 1 8 0 0 0 0<br>1 F F B F F   | SYSTEM ROM            |               | SYSTEM ROM            |               |  |

| 1 F F C 0 0<br>1 F F F 7 F   | SYSTEM I/O            | SYSTEM VO     | SYSTEM 1/0            | SYSTEM I/O    |  |

| 1 F F F 8 0<br>1 F F F B F   | DRAM I/O              |               | DRAM I/O              |               |  |

| 1 F F F C 0<br>1 F F F D F   |                       | INT REGISTERS |                       | INT REGISTERS |  |

| 1 F F F E O<br>1 F F F F F F | INT REGISTERS         |               | INT REGISTERS         |               |  |

PHILIPS

PHILIPS

Electronic components

## **BPCRT2-1**

Each BANK corresponds to a DRAM area and is associated with a CAS pin (CASN1-->CASN4).

The CSROMN pin is asserted when the SYSTEM ROM is decoded. During the 4 first CPU accesses the ROM shadowing technique places the ROM area in address 0 (see MEMORY SWAPPING).

BPCRT2 considers 2 types of external I/O :

The SYSTEM I/O for devices normally connected to the system bus

The DRAM I/O for devices hooked on the DRAM bus MD. If the address corresponds to these locations, the BPCRT2 will be transparent on address and data bus as for DRAM accesses.

In each case the CSION pin is asserted but the DTACK is generated only for the DRAMI/O (see DTACK generation).

The internal registers do not have the same mapping in SLAVE and MASTER modes to allow for independent access to 2 BPCRT2 with the same Chip Select.

In MASTER mode, TABLE 9 indicates the internal register map.

TABLE 9:

#### ACCESS ARBITRATION

The DRAM bus can be used by several masters on a cycle per cycle basis. An arbitration scheme is implemented to provide each master with a guaranteed access time. The various masters are:

- The system bus (CPU or DMA cycles)

- The display generator

- The refresh controller

- The optional drawing/manipulation coprocessor

The bus access is given with the following decreasing priority: Display generator, Refresh controller, and finally the system bus and the coprocessor which have the same priority.

When the display controller is active, the time is divided into slots of 16 clock periods (533 to 800 nS depending on the clock frequency) during which there is one window for the display controller and one for the system bus or the coprocessor. The display processor has always the first priority during the display window including during retrace if extra fetches are necessary for Image or Dynamic Control (if IC or DC bit =1). The system bus (CPU or DMA) and the coprocessor share the priority for the second window.

During the non display periods, the refresh controller has the first priority, the rest of time is for the system bus or the coprocessor. In order to limit the amout of wait states when the CPU or the Coprocessor access the memory, the sequence for DRAM access is resyncronized on the incoming requests.

PHILIPS

NOVEMBER

Electronic components

# **BPCRT2-1**

The system bus and the coprocessor can use windows which are not used by the other one. The system bus can for example avoid access to the DRAM if the drawing command given to the coprocessor is time critical.

Access to the System ROM (decoded and acknowledged by BPCRT2) is possible independently of this arbitration because it does not require access to the DRAM bus.

The PIXel ACceleration logic, being accessible from system bus and from DRAM bus, is a common memory mapped resource, , and so requires an arbitration when accessed. Nevertheless, no synchronization will be necessary when accessed from the system bus.

#### DTACK GENERATION

When a master of the system bus accesses the resources controlled by BPCRT2, the device will generate the acknowledge signal to allow the master to proceed. The access being synchronized on an available window, it may have to be delayed. Several modes are possible:

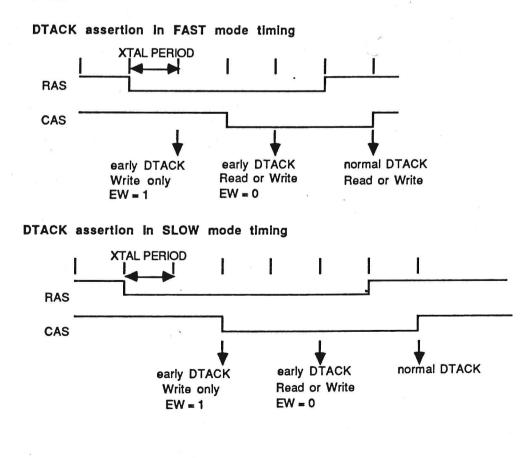

- The access to the DRAM will be acknowledged as soon as it is certain that the DATA will be available for the CPU. In order to shorten the bus cycle, DTACK can be asserted before the DATA is effectively valid (Early DTACK). If the ED bit in the CSR is equal to zero, a normal DTACK will be generated when the Data is valid on the system bus. If the ED bit is set, DTACK will be generated even two time slots before the early DTACK (66nS at 30 MHz) to speed up the CPU (or DMA for 68070). For a Write cycle, the DTACK can be generated 2 slots before if the bit Early Write EW, is set in the DCR register. The DTACK for a write can be advanced because the Address Strobe signal of the 680XX is not used by the BPCRT2. The following figure indicates the assertion time of the DTACK signal in the CPU window.

FIGURE 13:

PHILIPS

Electronic components

**BPCRT2-1**

- Access to the internal registers will be acknowledged immediately after arbitration against a potential access from the coprocessor.

- Access to the System ROM will be acknowledged after a programmable delay counted from the internal timing chain (5 possibilities depending on the DD, DD1 and DD2 bits of the CSR).

- The SYSTEM I/O device selection (CSI/O pin) is not acknowledged by the BPCRT2 but by the addressed device.

- The DRAM I/O are acknowledged as for the DRAM acknowledge, this device being considered completely synchronous with the access on the memory data bus MD.

#### **BUS ERROR GENERATION**

The BPCRT2 has a watch-dog timer function able to generate a BUS ERROR condition for the 68070. It is active when the BE bit of the Control register CSR is set to 1. When a resource is addressed on the system bus, (even if not controlled by the BPCRT2) by the assertion of UDSN or LDSN, the watch dog is incremented every video line . If the selection stays not acknowledged during two lines (64 to 128  $\mu$ S), the BERR signal is asserted to finish the current bus cycle and the BE FLAG bit is set in the CSR. The CPU will then enter a BUS ERROR exception routine which must test this status bit. The Read Status Register instruction will automatically reset the BERR FLAG and the BERRN pin.

The BERR pin of the BPCRT2 is an Open Drain buffer with an internal pull-up resistor.

#### RESET AND HALT GENERATION

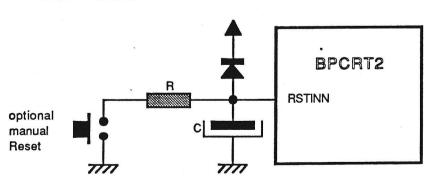

The BPCRT2 has a Reset input pin RSTINN, a Reset output pin RSTOUTN and a Halt output pin HALTN.

The Reset input is intended to be connected to a capacitor which will generate a low voltage at the begining of the Power-up period. It is detected and used to reset a Flip-Flop. When the on-chip crystal oscillator starts, the timing chain counts 8 frames and then clocks the Flip flop which releases the RSTOUTN pin. The HALTN pin is released one half line later. BPCRT2 is in the 20MHZ after activation of the Reset input pin, so delays on RSTOUTN and HALTN are compatible with a 680XX CPU whatever the XTAL frequency.

If a low voltage is applied again to the RSTINN input pin, the Flip-Flop will be reset, resetting the chip and provoking a complete new RESET sequence.

The RSTOUTN and HALTN pins of the BPCRT2 are Open Drain buffers with an internal pull-up resistor.

The diagram shows the basic reset circuit which is usable to reset the BPCRT2 and, via it, the rest of the system.

PHILIPS

FIGURE 14: RESET CIRCUIT

Electronic components

# **BPCRT2-1**

#### MEMORY SWAPPING

The 68070, like the 68000 has its vector table in the first kilobyte of memory starting from address zero. The RESET mechanism consists of fetching the Supervisor Stack Pointer and the initial Program counter in the first four words of the same area. It is often required that the Operating System is able to manipulate the Vector table contents to update or to dedicate a configuration.

The BPCRT2 has a built in swapping mechanism to allow for this feature.

When reset, the first four accesses (SSP and PC) will provoke the selection of the ROM area (CSN must be asserted). The ROM content will be routed to the processor (Address=H0 for SSP and Address=H4 for PC). After this sequence, the DRAM and the ROM will be decoded normally.

The user must for this purpose place the relevant values of the initial SSP and the initial PC at the beginning of the System ROM area (H180000).

### INTERRUPT GENERATION

The BPCRT2 can generate interrupts to the 68070 by asserting its INTN pin. This signal is intended to be routed to the INT1N or INT2N pin of the 68070 which uses a level sensitive without acknowledgment.

Each time the INTN signal is asserted, it generates an interrupt (of programmable level) in the 68070. The INTN pin is negated when the CPU reads the CSR status register.

Two conditions are able to generate an interrupt:

> The DCA mechanism can fetch an Interrupt instruction. This will set the IT1 bit in the CSR status register and assert the INTN pin. This mechanism allows for generating an interrupt every frame to synchronise the CPU operations.

> The PIXAC interface is declared free by the coprocessor (see PIXAC control registers). It will set the IT2 bit in the status register and assert the INTN pin. When the CPU read the CSR status register, the INTN signal is negated but the IT2 bit of the CSR remains high until the Pixel Accelerator is effectively used.

avoid the propagation on

NOVEMBER

1986

With the EN1 and EN2 bits of the CSR command register it is possible to disable the INTN pin for the respective IT1 and IT2 bits.

PHILIPS

Electronic components

### DRAM INTERFACE

The BPCRT2 has an on-chip Dynamic RAM control and drive circuit programmable for various types of currently available memory devices.

#### DRIVING MODES

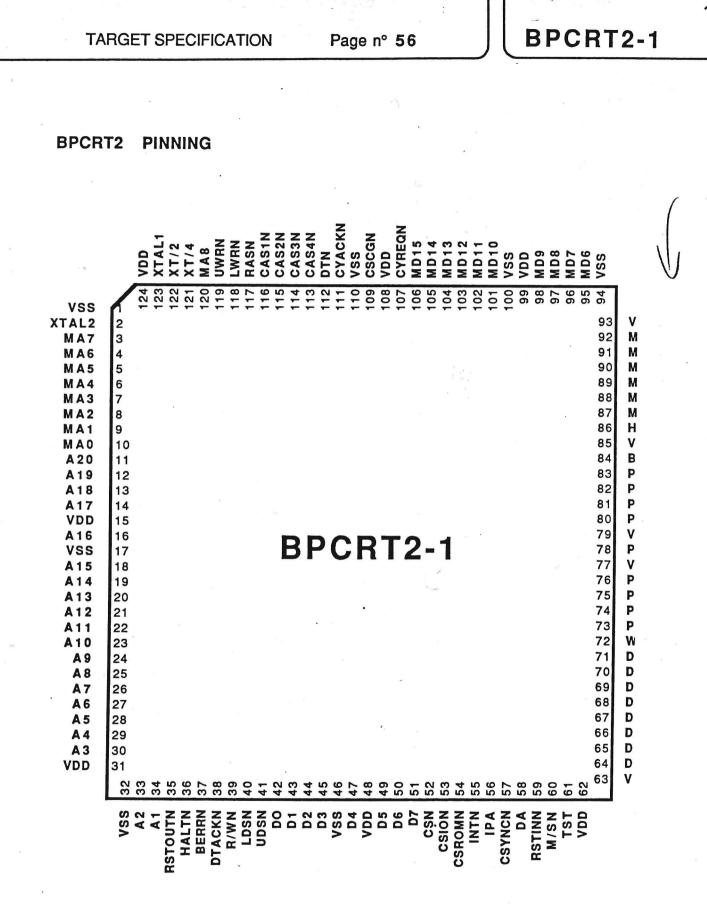

The BPCRT2 can drive directly up to 16 memory devices. It is possible to arrange them in one bank of 16 devices or in several banks of four devices.

Three or four CAS signals are available for the various banks.

The TYPE of DRAM (TD) bit in the Control/Status Register sets the DRAM interface for either 256K DRAMs or 64K DRAMs. In the first case, 9 multiplexed Address lines are generated and three CASN signals each select a bank of 512 KBytes.

In the second case, only 8 Address lines are available and the address decoding scheme is different. The fourth CASN signal is then available. In that mode it is possible to use one to four banks of four 64Kx4 devices.

The UWRN and LWRN signals control half of each bank to allow for instructions at the byte level.

When more than 16 devices are to be connected, external buffers must be used on MA0-8, UWRN, LWRN, CASxN and RASN signals.

When the coprocessor requires an access to the DRAM, the timing is still generated by the BPCRT2. The address is first transferred to BPCRT2 prior the RASN/CASxN sequence. The coprocessor then uses the DATA bus only (see COPROCESSOR INTERFACE).

### DRAM TIMING

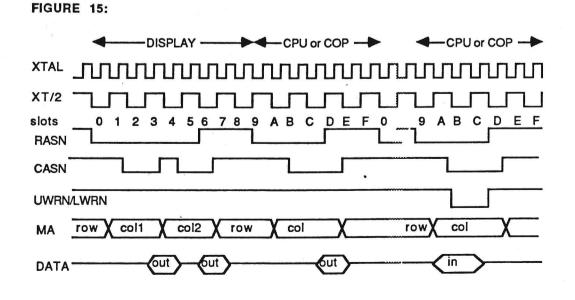

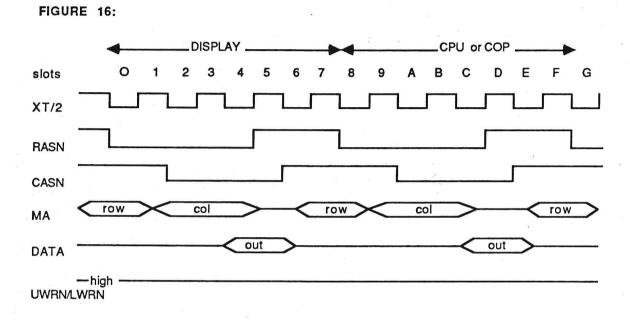

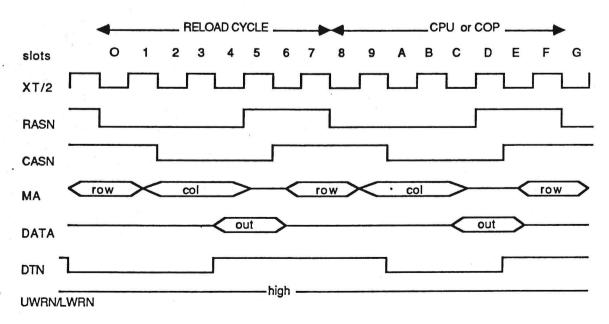

The Dynamic RAM interface timing is generated from the internal clock frequency produced from the on-chip oscillator. The basic cycle is a series of 16 time-slots, one time slot being a XTAL period.

During the display period, the ICA/DCA period and the refresh period, the basic cycle is divided in two parts, one window for the access of the internal address generator and one for the access of CPU or coprocessor. When using Dual-Port VRAMs, the 2 windows are for the CPU or the coprocessor during the display period, except for the first display cycle of each line, this cycle being used to reload the internal shift registers of the VRAM.

During non-display period, non-ICA/DCA period and non refresh period, the first window does not exist anymore, and the other window is triggered only when there is a CPU or coprocessor request.

The RASN/CASN timing is generated by using the 16 slots and resynchronizing with the internal clock before driving the buffers.

Two different timings are possible requiring different speeds of the DRAM devices:

- --> The FAST mode is optimized for NIBBLE mode DRAM devices with an access time of 120 nS at 27.5MHz clock. The FAST mode also permits the use of PAGE mode DRAM devices. The FAST mode timing allows to access 2 consecutive 16-bit words using 9 slots. The remaining 7 slots are used to generate an access for the CPU or the Coprocessor. This FAST mode is also necessary when using double resolution images. The RAS is always generated in this case even if there is no CPU or coprocessor request.

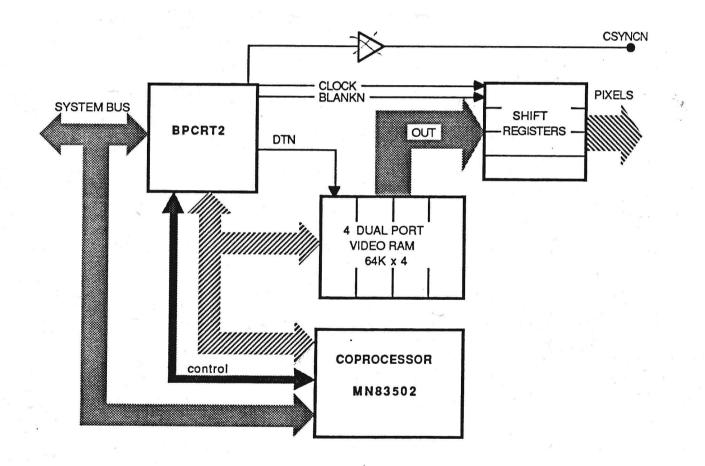

- --> The SLOW mode is based on two normal (single) accesses each using 8 slots. Only one 16-bit word is read for the display controller part which is enough for the single resolution and 4 bits per pixel. The speed of the DRAM devices can be lower in this case. Dual port Video RAMs are also driven using this mode. No RASN and CASxN are generated for the CPU window if there is no access request from the CPU or the coprocessor.

PHILIPS

NOVEMBER

100/

Electronic components

# **BPCRT2-1**

Different addressing schemes and slightly different timings are generated to drive the Nibble mode, the Page mode or the Dual ported Video Ram devices. Two bits of the Control/Status Register (DM1-2) can be set accordingly to the type of device effectively used:

| DM1 | DM2 | TIMING SPEED | DRAM SUPPORTED     |

|-----|-----|--------------|--------------------|

| 0   | 0   | SLOW         | NORMAL MODE        |

| 0   | 1   | FAST         | PAGEMODE           |

| 1   | 0   | FAST         | NIBBLE MODE        |

| 1   | 1   | SLOW         | DUAL PORT VIDEORAM |

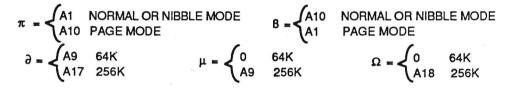

The correspondance between Memory Address bus MA and CPU Address bus A is as follows:

| TABLE<br>10 |      | MAO | MA1        | MA2 | МАЗ        | MA4        | MA5        | MA6 | MA7        | MA8 |

|-------------|------|-----|------------|-----|------------|------------|------------|-----|------------|-----|

|             | RASN | π   | <b>A</b> 2 | AЗ  | <b>A</b> 4 | <b>A</b> 5 | <b>A</b> 6 | A7  | <b>A</b> 8 | μ   |

|             | CASN | B   | A11        | A12 | A13        | A14        | A15        | A16 | 9          | Ω   |

The DUAL PORT mode has the same MA configuration as the NORMAL mode but the addresses valid on RAS are valid on CAS, and vice versa. For the NIBBLE mode DRAMs MA0 and MA8 have to be crossed externally.

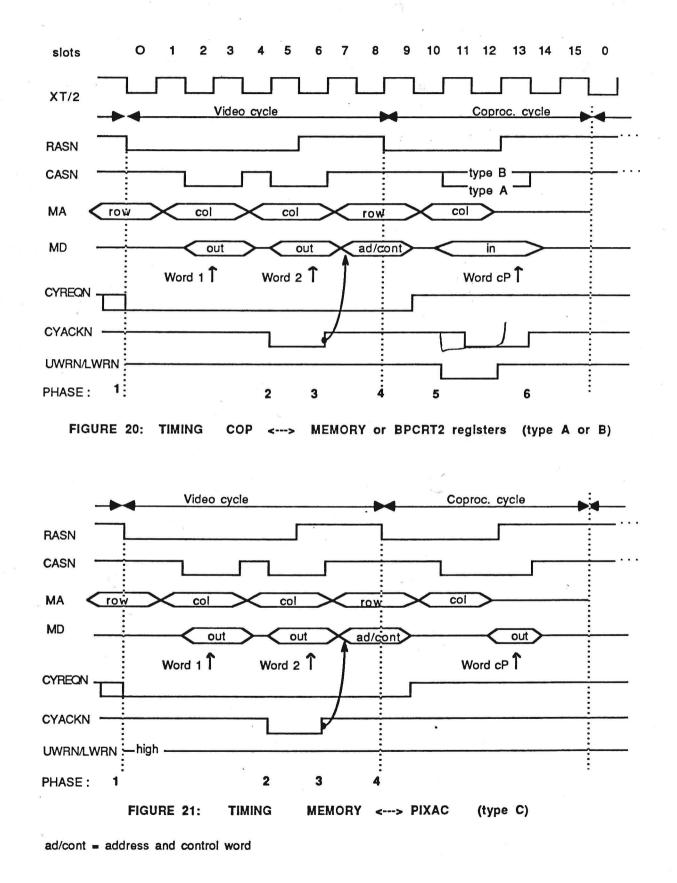

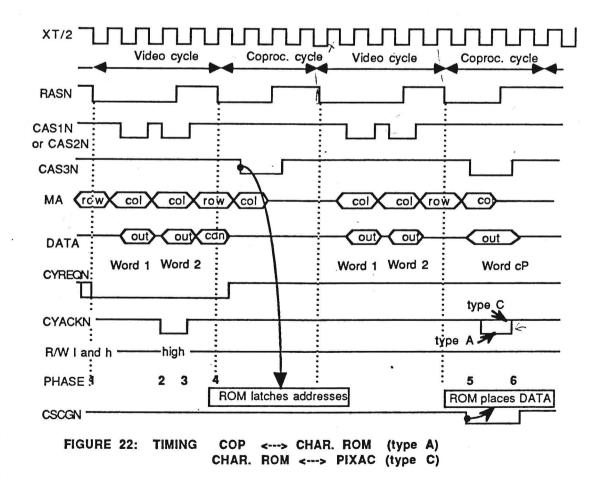

FIGURE 15 shows the window timing in the FAST mode. The first window is a display window followed by a CPU read cycle then by a CPU write cycle. In the display window the column 2 is not generated for the NIBBLE mode DRAM but is automatically generated for the PAGE mode DRAM.

PHILIPS

PHILIPS

Electronic components

FIGURE 16 represents display and CPU windows in SLOW mode. The CPU (or coprocessor) access is a read cycle.

FIGURE 17 represents the beginning of a display line when using DUAL PORT videorams. The first access for the line is for reloading the internal shift registers. For that, the DTN signal is asserted one time slot before the falling edge of RAS and it rises one time slot before the rising edge of RASN. The rest of the time DTN=CASN and the windows, except for the refresh and the ICA/DCA part, are all given to the CPU or the coprocessor, increasing the access transparency. In this timing chart the CPU access is a read cycle.

DH

NOVEMBER

PHILIPS Electronic components

# **BPCRT2-1**

#### DRAM REFRESH

The refresh of the DRAM is made during the display time simply by connecting the LSBs of the video scan counter to the ROW addresses of the DRAM. During the vertical retrace period, the BPCRT2 will generate 4 refresh cycles during the horizontal retrace. A special Refresh counter is used for this.

In Physical screen mode, the addresses are scanned consecutively during the display active period so this principle assures that the 256 rows of the memory will be refreshed every 4 mS. When using subscreens by reloading the VSR register, one of 2 consecutive subscreens must have at least 4 lines to insure the memory refresh.

In Logical sreen mode the addresses are generated more randomly. Four refresh cycles are then generated during each horizontal retrace. 1 22.1

MOLAIC 2013 RUN-LENGTH For

### DRAM DESELECT.

During the RESET period, the CASxN output pins are three-stated in order to test if a memory bank is effectively connected to the device. If a zero is present (pin grounded via a resistor), the bank will be disabled and the DTACKN will not be generated. Eventually, if no DTACKN is generated by another slave or memory, the watch-dog timer will generate a BERR. All the CASxN pins are tested following this principle.

The BANK selection has an influence on the ICA pointer as indicated in this table :

| TABLE 11    | 256               | <                  | 64K    |           |  |  |  |

|-------------|-------------------|--------------------|--------|-----------|--|--|--|

|             | BANK 1<br>enabled | BANK 1<br>disabled | MASTER | SLAVEDUAL |  |  |  |

| ICA POINTER | H400              | H80400             | H400   | H80400    |  |  |  |

In 256K mode, the address H80400 is in the BANK 2, this means that BPCRT2 must have BANK 1 or BANK 2 enabled when using ICA.

In 64K mode, the address H80400 is in BANK 1 for the SLAVEDUAL BPCRT2 (see ADDRESS DECODING), this means that the MASTER and SLAVEDUAL BPCRT2 must have by necessity BANK 1 enabled to use ICA.

PHILIPS

NOVEMBER

Electronic components

# BPCRT2-1

### PIXEL ACCELERATOR

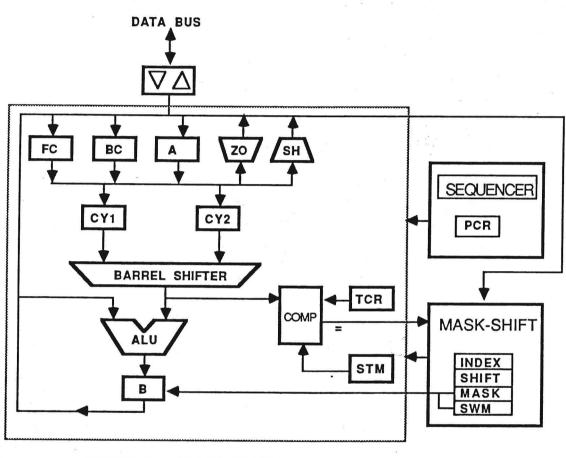

### **PIXAC GENERAL DESCRIPTION**

The Pixel Accelerator logic is specific hardware available to speed up the manipulation of pixel contents in memory. It is usable under host control as a memory mapped slave interface or under control of the coprocessor via the coprocessor interface.

The main functions of the PIXel ACcelerator (PIXAC) are:

- alignment of source words onto destination words using a barrel shifter

- test-of-pixel-content-and-modify

- masking of the destination pixel

- logical operations

- bit-to-pixel and pixel-to-bit transformations

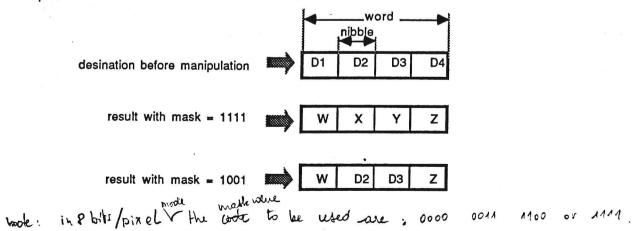

The PIXAC is intended to work for 4 bits per pixel and for 8 bits per pixel memory organisations. The manipulations are always done on a 16-bit word basis, so 4 pixels or 2 pixels are processed at a time.

Special masks are available to act selectively on one or several bits of each pixel. This feature is specially useful to transcode from plane per plane organized images to the memory organisation used by BPCRT2 or in the reverse way.

The PIXAC needs a software or a firmware layer to perform its operation. It is no more than a high speed logic unit specialized in nibble or byte manipulations.